Verilog 学习笔记(0)——绪论

绪论

硬件描述语言(HDL)

当你需要设计一个数字电路系统的时候,往往需要记录下这个设计以使:

- 你之后(或许几天或许几年)仍能看懂这个设计

- 其他人也能看懂并理解这个设计

- 这个设计能被仿真并且验证

- 这个设计能够被解析到门级等低层次的电路描述(综合,Synthesize)

- 它能被做出来并实现功能

表示硬件的几个方式:

- 画电原理图

- 手画

- 电子辅助设计(EDA)画

- 写网表描述电路元件连接关系

写布尔表达式

$AAA=abc+def$

使用硬件描述语言(Hardware Description Language)

assign overflow = c31 ^ c32;

关于 HDL 的历史略过不谈,反正 Verilog 作为 HDL 之一现在是 IEEE 标准。

注意区分 HDL 和编程语言的区别:

最明显的区别,编程语言描述存在运行的先后逻辑顺序,而硬件描述语言只是表示不同模块之间的连接关系而不存在先后顺序,也没有一个运行的起点。同时硬件描述语言中也不存在类似于循环的按步运算的方式。

Verilog 语言与C 语言之间有很多相似之处,借鉴了许多语法,如预编译指令和一些高级编程语言结构,但仍有许多区别:

- 互连:硬件系统中互连是非常重要的组成部分,Verilog 的 wire 型变量配合一些驱动结构能够有效地描述出网线的互连。

- 并发:C 语言是串行的,机器指令基本顺序执行;Verilog 可以有效地描述并行的硬件系统。

- 时间:运行 C 程序的运行时间主要取决于处理器本身的性能;而 Verilog 语言定义了绝对和相对的时间度量,仿真时通过时间度量与周期关系描述信号之间的时间关系。

评判一段 HDL 语言的优劣与软件语言实际上不大相同,在评价设计的代码时,优先考虑的是该设计的最终性能,主要是所转化成的硬件电路的面积和运行速度,而代码水平较高仅仅是该设计由硬件转化为 HDL 语言较为流畅。在初学时,最好对硬件结构的连接了解的较为透彻后再用适当的 HDL 语句将其表达出来,而不是片面追求代码的整洁、简短(当然能兼得最好)。

HDL 的设计和验证

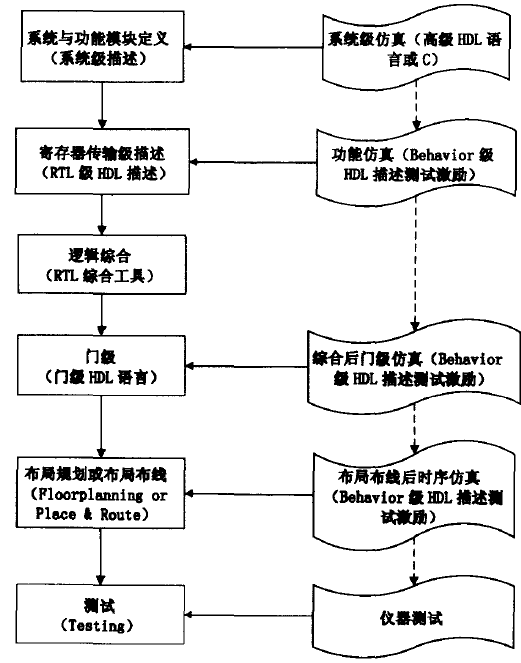

如图所示,HDL 需要逐级设计与仿真。

稍作叙述相关的设计步骤和概念:

- 系统与功能模块定义

略

行为级描述测试激励(Behavior Level)

明确所有模块之间的接口和边界。模块内部的功能已经明确,模块间的所有接口以及顶层的输入输出信号在行为级已经被描述出来。寄存器传输级(RTL,Register Transfer Level)

RTL 指不关注寄存器和组合逻辑的具体细节(使用了多少逻辑门以及门之间的连接关系),通过描述寄存器之间的逻辑功能来描述电路的 HDL 层次。RTL 是比门级高的抽象层次,最大特点是可以直接用综合工具综合为门级网表。RTL 设计直接决定着设计的功能和效率。对 RTL 级描述进行功能仿真

一般要对 RTL 级设计进行功能仿真,仿真的目的是验证 RTL 级描述是否与设计意图一致。为了提高效率,功能仿真的测试激励一般使用行为级的 HDL 语言描述。逻辑综合(使用 RTL 级 EDA 工具)

RTL 级综合指将 RTL 级 HDL 语言翻译成由与、或、非门等基本逻辑单元组成的门级连接,并根据设计目标与要求(约束条件)优化所生成的逻辑连接,输出门级网表文件。门级(Gate Level)

基本都依靠专业综合工具实现从 RTL 到门级的转换。目前要直接使用门级描述的情况主要是设计中有面积或时序要求较高的模块。门级描述的特点是整个设计使用逻辑门实现,通过逻辑门的组合显化描述设计的引脚、功能和时钟周期等信息。综合后门级仿真

综合完成后检查综合结果是否与设计一致。仿真时,把综合生成的标准延时文件反标注到综合仿真模型中,以估计门延时的影响,但不能估算线延时。布局规划与布局布线

略布局布线后的时序仿真和验证

将最终布局规划或布局布线的延时信息反标注到设计网表中所进行的仿真就叫时序仿真或布局布线后仿真,简称后仿真。它能较好反应芯片的实际工作情况,确保设计的可靠性和稳定性。主要目的在于发现时序违规(Timing Violation),即不满足时序约束或器件固有时序规则(建立时间、保持时间等)的情况。

VSCode 中的 Verilog 相关配置

Vivado 我还没装之前用的都是 ISE 等我装了 Vivado 再补安装过程(躺

No Comments