Verilog 学习笔记(2)——ModelSim 的基本使用

ModelSim 的基本使用

在上一章中我们已经介绍了 ModelSim 的基本用途与安装,这章介绍 ModelSim 的基本使用方法。

如何在 ModelSim 中建立工程并完成仿真

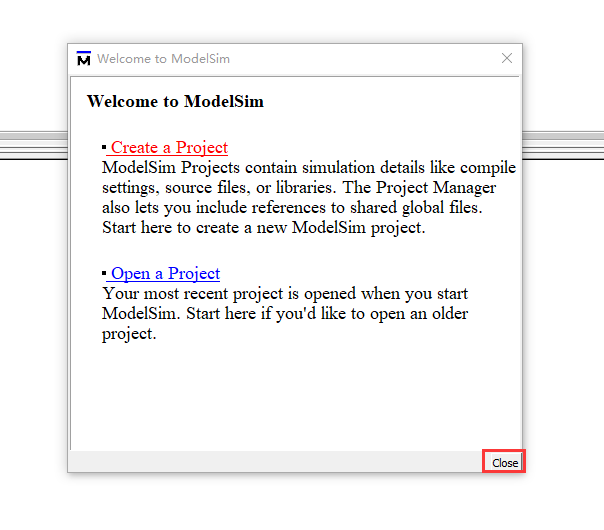

一开始会弹出 Welcome 的窗口,我们先 Close。

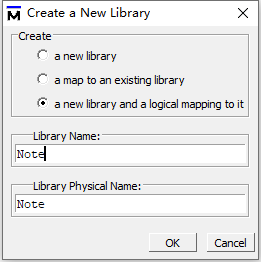

在 File->New->Library 先建立一个自己的库。

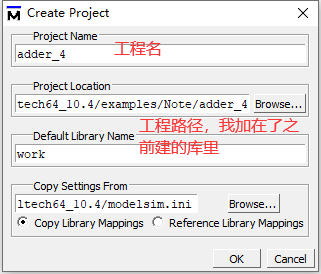

然后就可以新建工程了(之后打开也可以在前面关掉的 Welcome 窗口新建或打开工程)

点击 File->New->Project 建立工程,在对应的地方输入工程名,选择工程存储路径,输入库的名称(并不是前面建的库,而是这个工程所要用到的实例化的库),我以一个四位加法器为例。

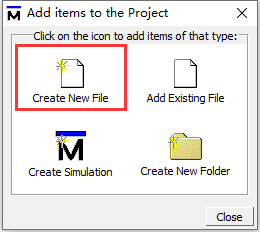

选择 Create New File

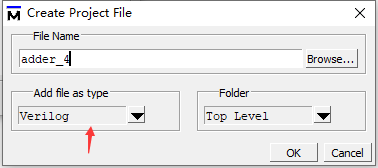

命名就随便写,语言记得改为 Verilog(默认是 VHDL)。

像上一章提到的,为了仿真还要建立一个 Testbench,重复以上步骤新建一个 Testbench。

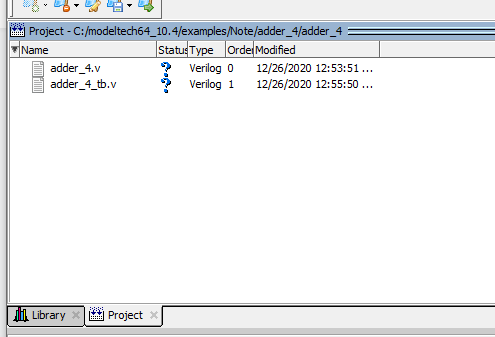

建立完了以后应该是如图所示有两个.v 格式的文件。

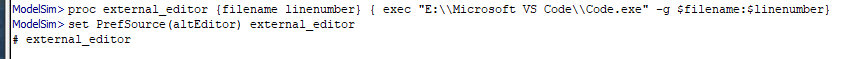

双击之后就可以开始编辑了,一般来说应该是默认的内置编辑器,如果想用 VSCode 编辑的话,先按照绪论里的布道指南配好 Verilog 插件,然后在 Transcript 窗口(如果没有的话 View->Transcript)里输入

proc external_editor {filename linenumber} { exec "{{VSCode路径}}\\Code.exe" -g $filename:$linenumber}

回车,输入

set PrefSource(altEditor) external_editor

即从默认的内置编辑器改为用 VSCode 打开。

若要改回默认的编辑器,则在 Transcript 窗口输入

unset PrefSource(altEditor)

在.v 文件中输入相应的 Verilog 代码,不过我还没讲怎么写,所以先看看就好。

adder_4:

module adder_4(

input [3:0] A,

input [3:0] B,

output [4:0] sum );

assign sum = A+B;

endmodule

adder_4_tb:

`timescale 1ns/1ns

module adder_4_tb();

reg [3:0] A;

reg [3:0] B;

wire [4:0] sum;

initial begin

A = 0;

B = 0;

#10;

A = 4'b0110;

B = 4'b1010;

#10;

A = 4'd3;

B = 4'd7;

#10;

A = 5;

B = 8;

#10;

A = 4'he;

B = 4'ha;

#10;

A = 4'hf;

B = 4'hf;

end

//initial begin

// #100 $finish;

//end

adder_4 adder0(

.A(A),

.B(B),

.sum(sum)

);

endmodule

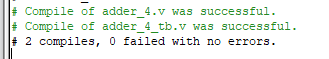

然后菜单里 Compile->Compile all 或者右键文件 Compile ,在 Transcript 里会有编译结果(如果有错就要 debug 不过我这两条应该没有问题)

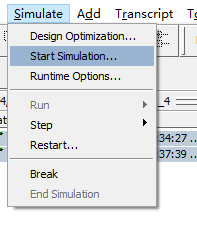

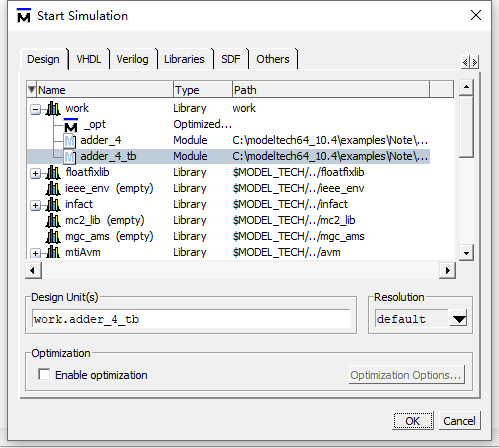

之后就可以进行仿真了,菜单 Simulate->start simulation ,选择建立的 tb 文件,把 Enable optimization 框选去掉

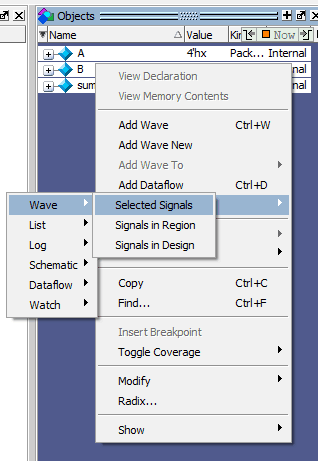

在 object 窗口里选择想要仿真的信号,右键->add to->wave->selected signals 来加入波形

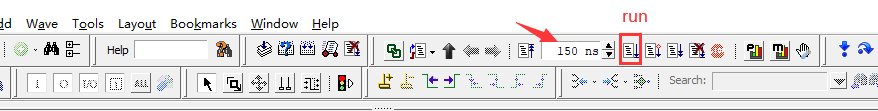

在上方工具栏 Run,我这里跑150ns

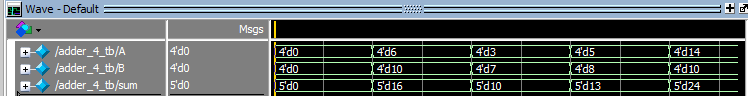

出现如图波形,如果觉得在这个窗口看不方便可以点击箭头所指按钮把 Wave 窗口独立,另外右键信号->Radix可以更改进制和符号,最终实现如图

符合四位加法器的功能,验证通过。至此功能仿真完成。

使用 ModelSim 的一些快捷键

下一章就可以开始正经的 Verilog 了。。。

No Comments