Verilog 学习笔记(8)——应用:人体反应测试仪

人体反应测试仪

一·设计规划

1.设计要求

设计一个人体反应测试仪,用4个8段LED作为显示(当然也可以用其他的显示方式,比如可以使用VGA或其他的显示器),2个按键分别表示启动(START)和反应按键。 Start键表示开始测试,内部计数器开始计数,三个8段显示为————,接着随机时间(500ms到5S不等)变为||||,被测试的人看到后快速按反应按键,测试仪显示从开始变为||||到被测试人按反应按键的时间,即为被测试人的反应时间,该反应时间的分辨率为1ms,所以最大可测试时间为9999ms,但是注意,如果此时间为负或小于人体最小反应时间(100ms),则测试为Fail(显示FaiL)。

如果搞一些音效,则更佳。

提示:

1、随机时间要足够随机,不能让被测试的人有预判。

2、按键有2个,为什么不用一个,请考虑按键去毛刺的功能。

以上设计使用TOP DOWN 设计流程,需要完成系统框图设计、RTL设计、综合、功能和时序仿真、物理实现。如果有FPGA实现板则更佳

2.设计思路

首先考虑顶层,需要 4 个 8 段 LED 来作为显示,需要显示的信息有表示初始状态的 0000,表示开始状态的 —-,表示随机时间后的||||,以及测试完毕后的反应时间或 FAIL信息。

考虑三个按键,一个复位按键,一个开始按键,一个反应按键。

当每次测试完后按复位按键可以恢复到初始状态,按下开始按键后变为—-,经过随机事件后变为||||,若在100ms以内按下反应按键或9999ms以外变为FaiL,否则显示随机时间后与按下反应时间之间的时间差。共需要复位、开始、反应、显示时间、显示错误五个状态。

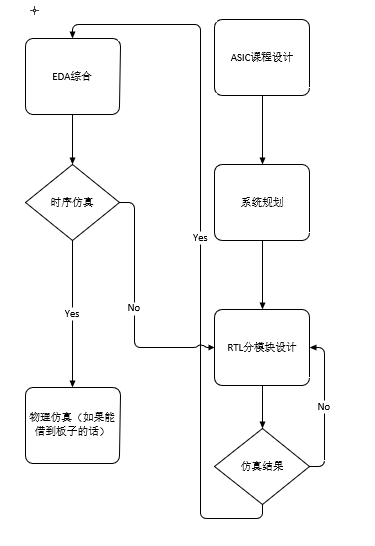

3.设计流程图,设计平台,EDA使用说明

设计流程图如上

设计平台如下:

- 仿真工具:Vivado

- EDA 工具:Vivado

- FPGA 开发板:Xilinx Aritx-7

- FPGA 芯片:XC7A100T-1CSG324C(由于疫情的原因,最终没有借到板子和芯片,无法物理上板测试)

二·设计实现

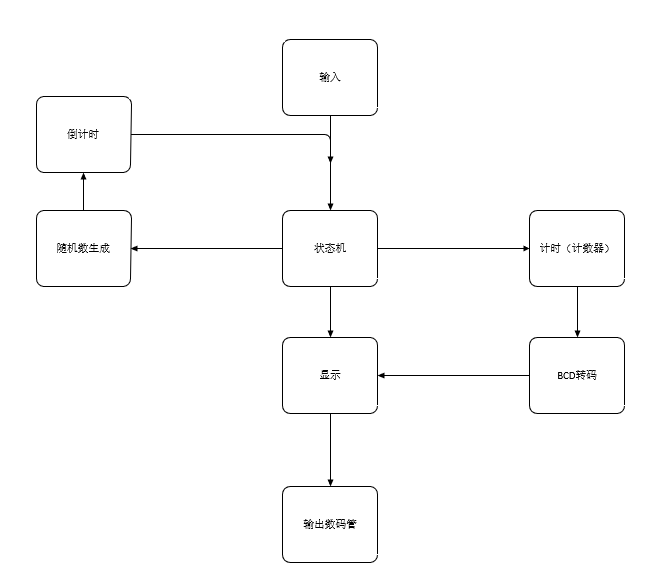

1.框图介绍

整个设计需要考虑输入模块、随机数生成模块、计数模块、转码模块、显示模块以及状态机,最后的框图如下

2.各模块设计和验证(仿真激励和结果波形说明)

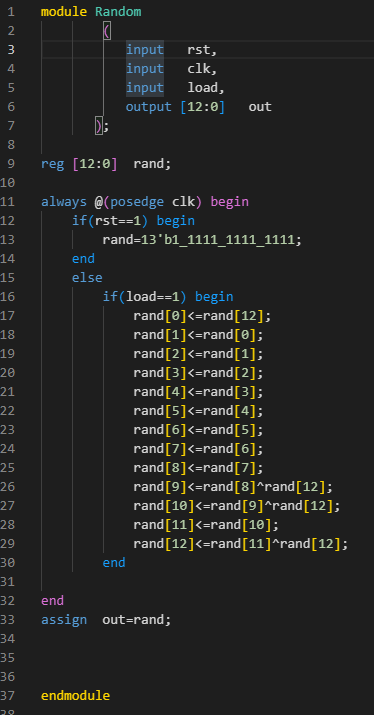

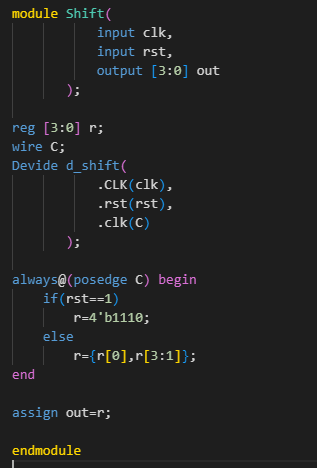

(1)随机数模块

要求随机时间从 500ms 到 5s 不等,分辨率为 1ms,即需要生成 500-5000 的随机数。

考虑使用 LFSR 生成伪随机数。$5000-500+1=4501<2^{13}$ ,需要产生 13 位的随机数。g序列采用13‘b 11011000000001seed 直接取 13‘b 1111111111111 产生伪随机表代码如下

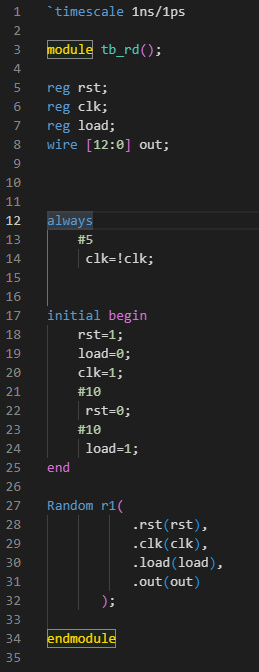

testbench如下

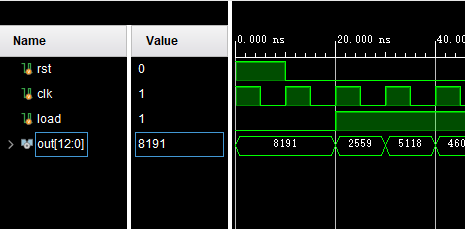

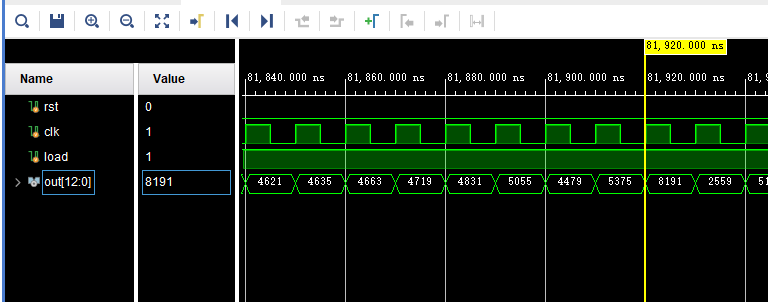

功能仿真波形如下

由于采取了13位,100 MHz时钟,在 81920 ns 内生成一整个从 0-8191 的序列,功能仿真验证正确。

最后改写代码,将结果 %4501+500即可得到指定范围

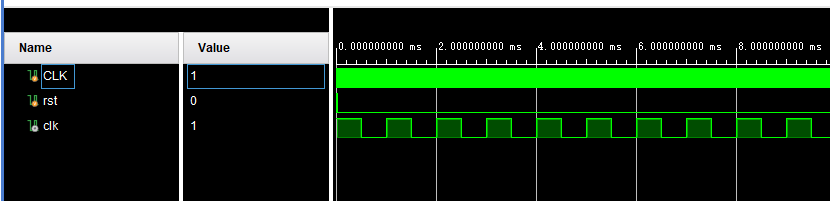

(2)分频器

FPGA 自带晶振时钟信号为 100MHz,通过分频器做到 1ms 分辨率,即 1000Hz ,只需要周期放大 $10^5$ 倍即可。

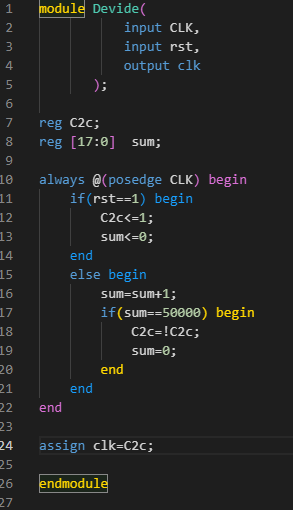

代码如下

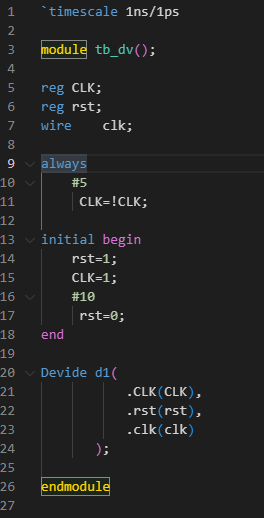

testbench 如下

仿真结果如下

分频后的时钟周期为 1 ms ,功能正确符合要求。

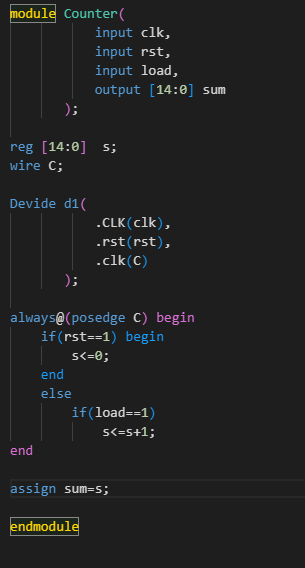

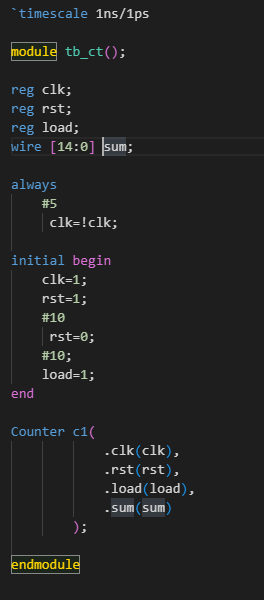

(3)计数器

记录时钟跳变的次数,即计时器。

由于需要从 1 计数到 9999 以上,选择14位

代码如下

testbench如下

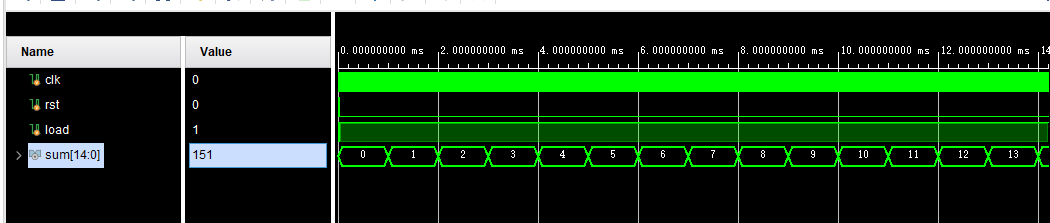

功能仿真如下,可以正常计时

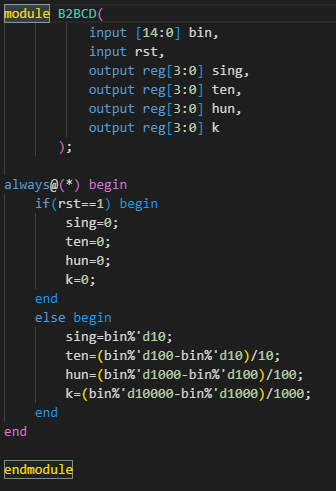

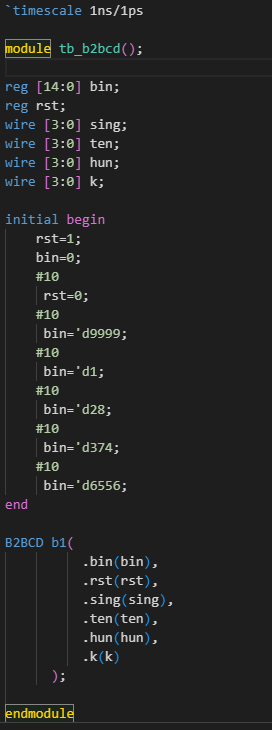

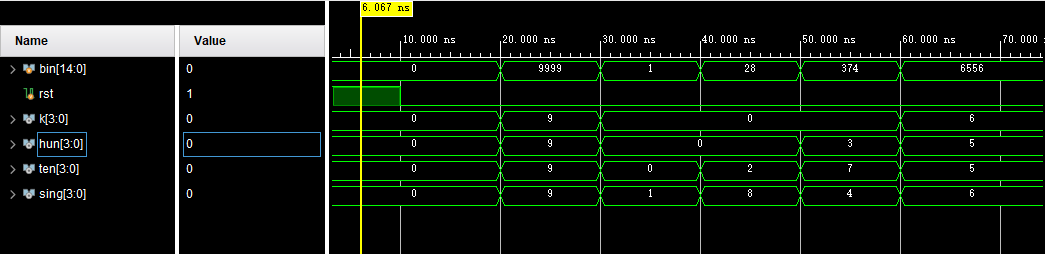

(4)BCD转码器

由于计时器的信号为二进制码,需要通过 BCD 转码得到十进制码

代码如下

testbench如下

testbench选取了最小值、最大值、一位数、两位数、三位数、四位数、各位包含1234567890来进行验证,验证结果如下

功能正确。

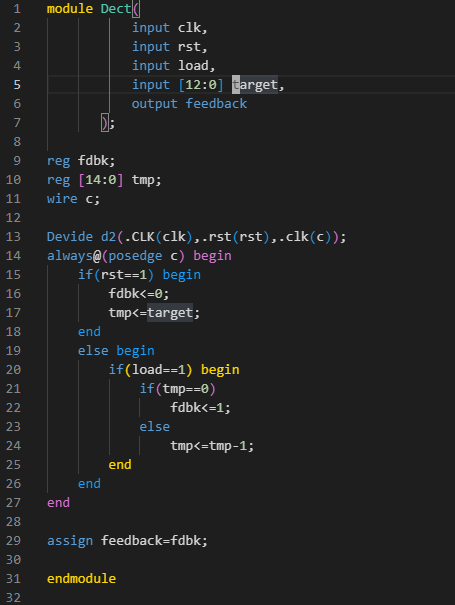

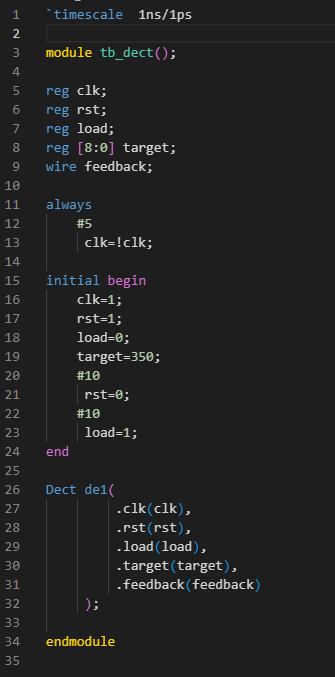

(5)倒计时器

要求在输入目标信号并开始计时,达到指定时间后输出反馈信号。

代码如下

testbench如下

仿真结果如下

由于分频后的时钟精度为 1ms,因此虽然设定目标是 350 ms却在 351 ms 发出信号,但该倒计时器的目的是根据随机数发出信号,因此 1ms 的固定延迟并不会影响随机的信号发出,倒计时器功能正确。

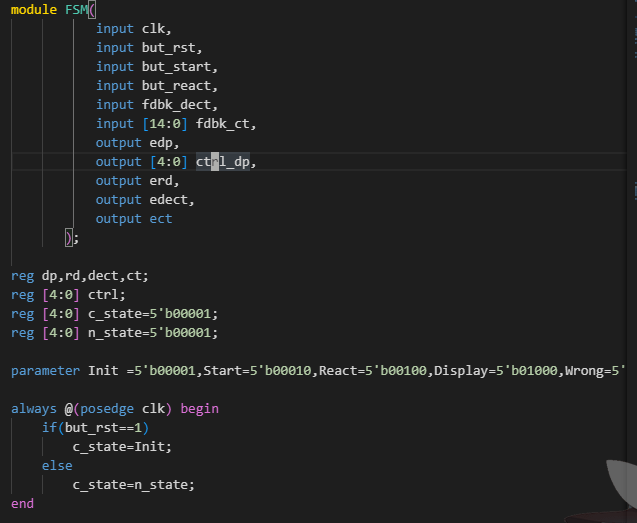

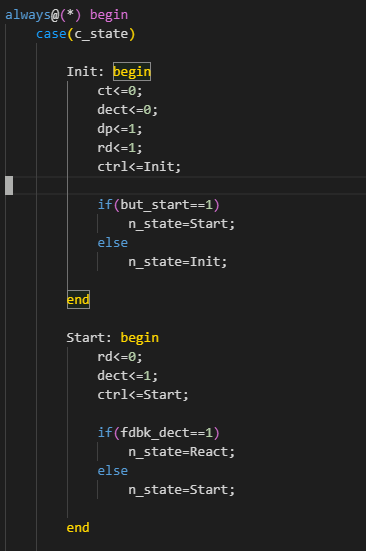

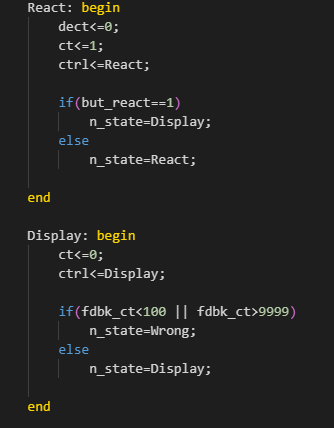

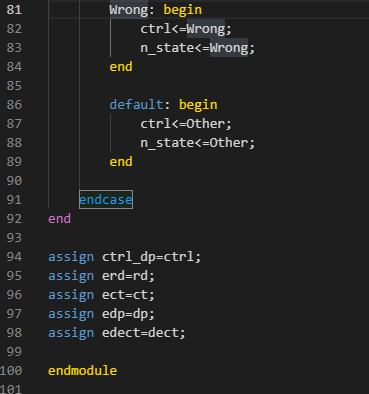

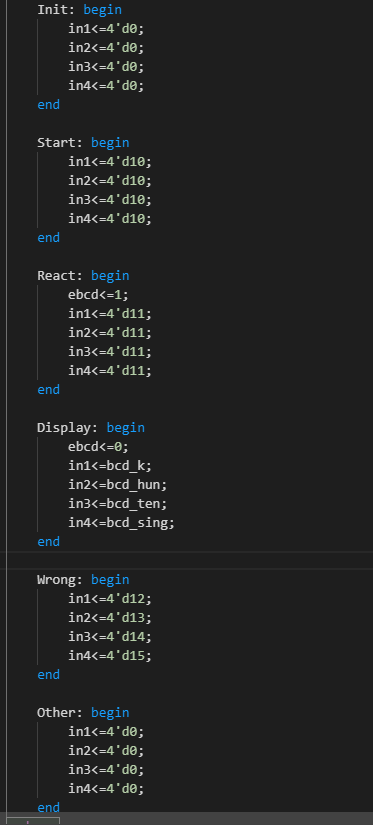

(6)状态机

根据前文所述,需要设计复位、开始、反应、显示、错误五个状态,考虑用独热码编码,同时为了防止预期外的情况另设一其他状态 5’b11111

复位、开始、显示状态分别由三个按钮触发,反应为开始后经过随机时间进入的状态,错误为显示的时间差大于9999或小于100时触发。

代码如下

基本的端口设置以及状态的转移

复位信号转移到初始状态,打开随机数生成和显示模块,关闭计数和倒计时。若开始按钮按下则进入开始状态。

开始状态关闭随机数生成,打开倒计时模块。若倒计时结束接收到反馈信号进入反应状态。

反应状态打开计时模块关闭倒计时模块,若接收到反应按钮信号进入显示状态。

显示状态关闭计时模块,接受及时反馈,若反馈在范围外则进入错误状态。

错误状态和其他状态。

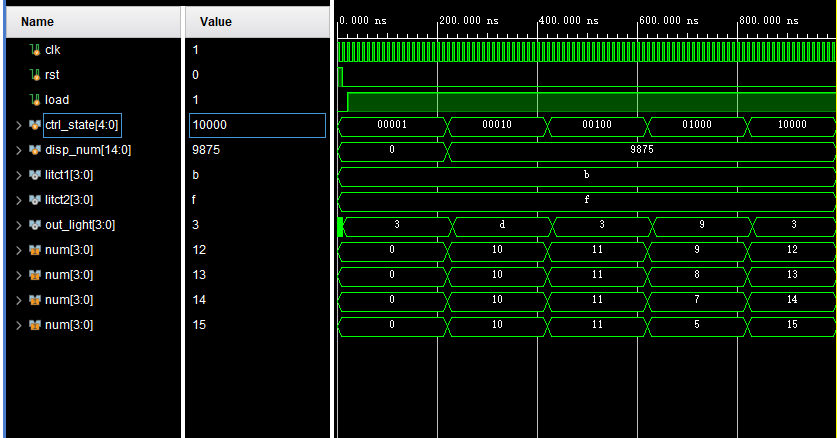

仿真如下,设定为 0.1ms 按下开始,随机到的倒计时为 510ms,之后过了 400ms 按下了反应按钮

满足功能,小数点后的数字为 testbench 设定

下面验证反应时间在预期外的情况

进入了 Wrong 状态

满足验证

testbench 代码将放在附件

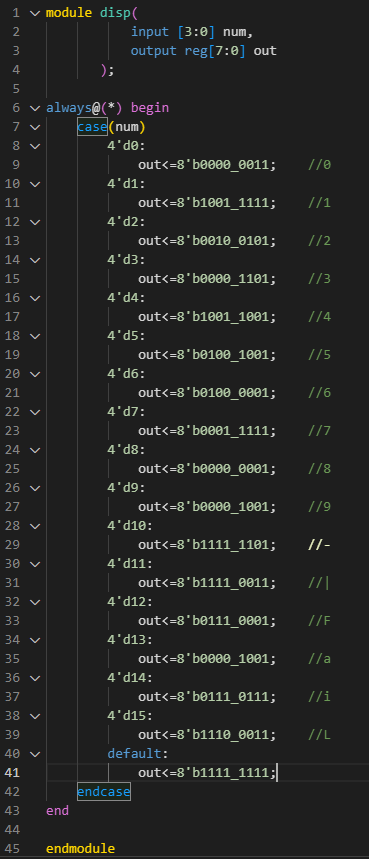

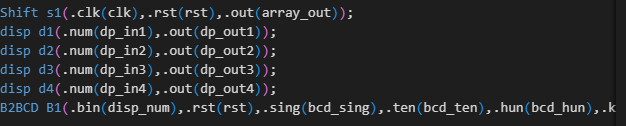

(7)显示模块

需要将转化出的 BCD 码转化为七段数码管显示。

复位状态需要显示“0000”

开始状态需要显示“—-”

反应状态显示“||||”

显示状态显示对应数字

错误状态显示“FaiL”

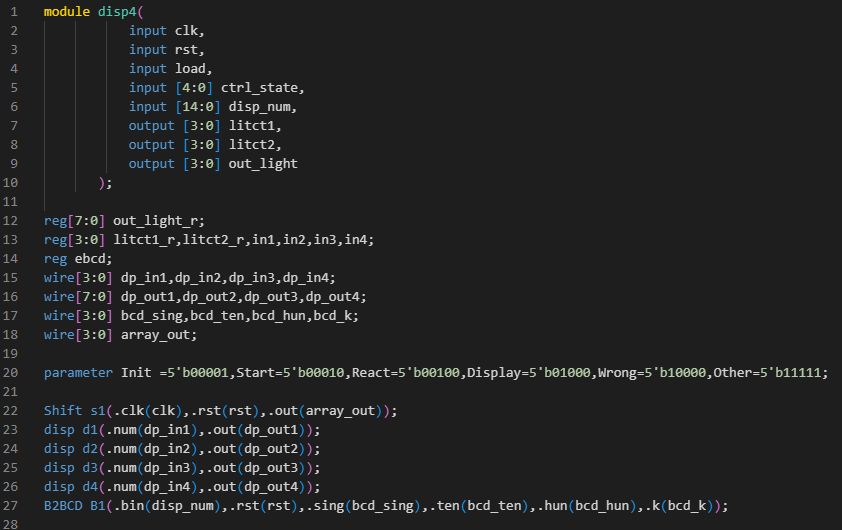

同时该 FPGA 板有8个晶体管共阴极连接,因此需要屏蔽左边四个晶体管,右边晶体管不断切换。

晶体管代码如下

转换器代码,由于晶体管不能同时亮,所以需要设定转换来达到视觉中同时亮的效果

最后的4位晶体管显示将上述模块组合,

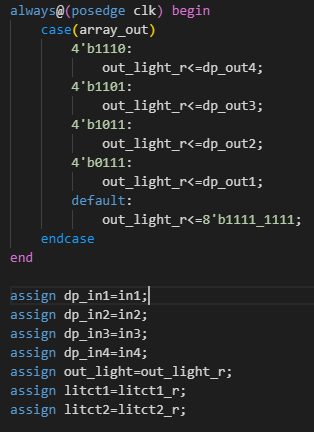

如图根据状态显示晶体管的数,通过转码器和晶体管显示器转化成七/八段码

最后根据状态切换选择输出的晶体管避免共阴极不能同时显示的问题。

晶体管在五个状态的显示结果都正常,显示模块功能正确

初始状态显示4个0,开始状态显示4个-,反应状态显示4个|,显示状态显示对应数码,错误状态显示FaiL对应编码。

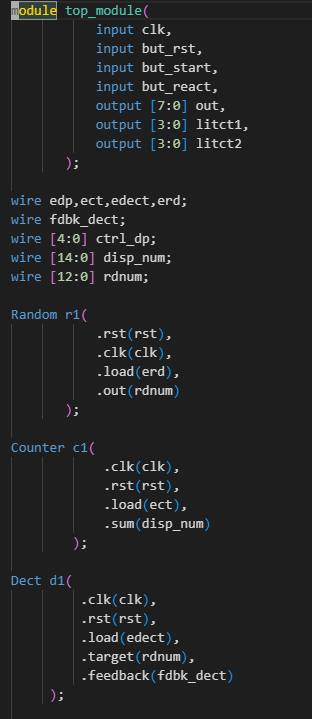

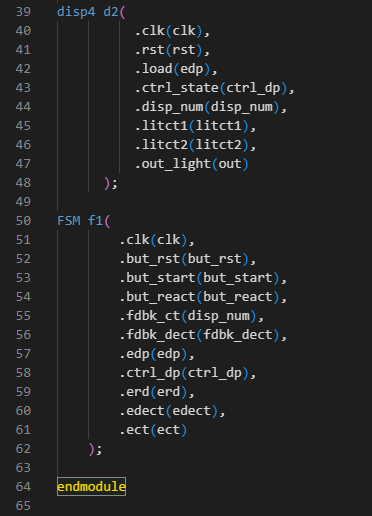

(8)top_module

顶层封装,代码如下

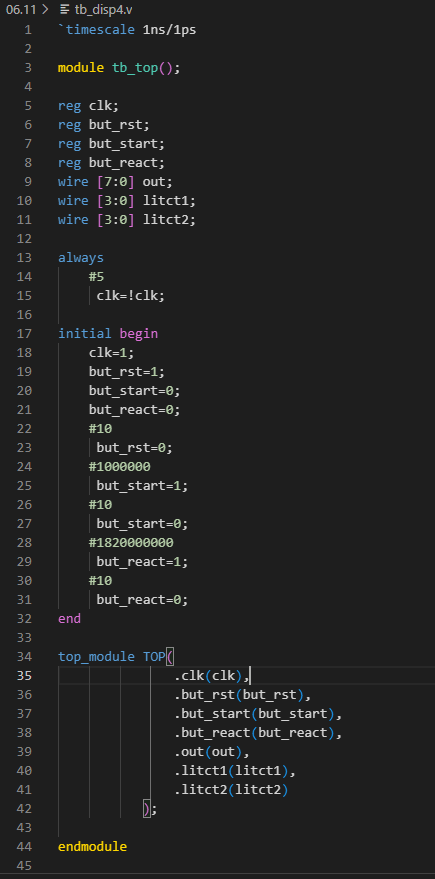

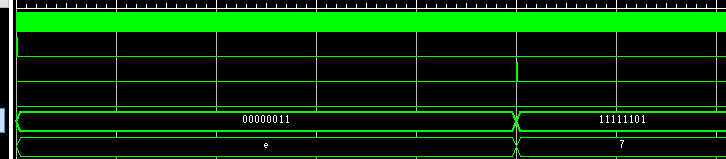

testbench如下

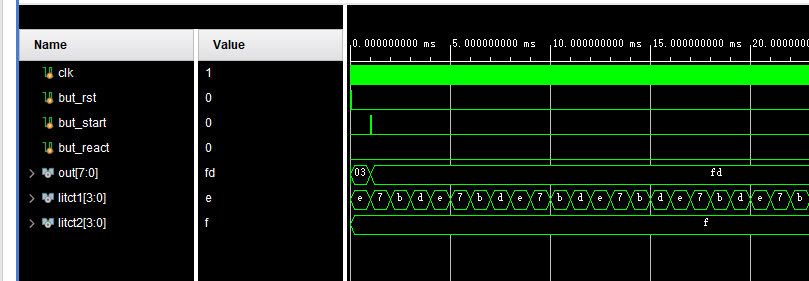

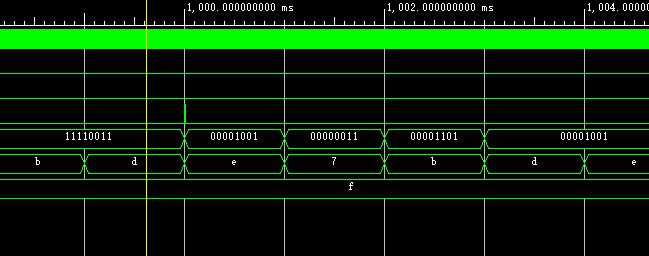

可以发现复位后右边四个晶体管数字循环使能,左边晶体管不亮,复位后右三管显示00000011即数字0,开始后显示11111101即-

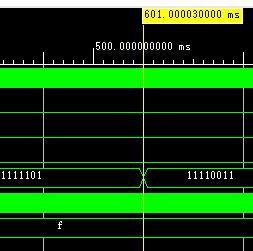

由于随机数在500-5000的范围,100MHz情况下testbench难以设置过大的 react 信号,故将随机数设置为500 ms进行仿真

进入反应状态后七段码变为11110011,即|

反应之后则是四位数字循环显示,对应下面的显示管,功能正确。

后续综合上板由于疫情没整到板就没了。

No Comments